# **OpenFPGA Documentation**

Release 1.2.2022

Xifan Tang

Apr 20, 2024

# **OVERVIEW**

| 1 | 1.1       Fully Customizable Architecture         1.2       FPGA-Verilog         1.3       FPGA-SDC         1.4       FPGA-Bitstream                                                                     | 1<br>2<br>3<br>3<br>4<br>4                   |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2 | 2.1       Supported Circuit Designs         2.2       Supported FPGA Architectures                                                                                                                       | 5<br>7<br>8<br>8                             |

| 3 | 3.1       How to Compile         3.2       OpenFPGA Shell Commands         1                                                                                                                             | 9<br>9<br>15                                 |

| 4 | 4.1 Generate Fabric Netlists       1         4.2 From Verilog to Verification       1                                                                                                                    | 17<br>17<br>18<br>21                         |

| 5 | 5.1       A Quick Start       2         5.2       Integrating Custom Verilog Modules with user_defined_template.v       3         5.3       Build an FPGA fabric using Standard Cell Libraries       3   | <b>23</b><br>23<br>35<br>39<br>48            |

| 6 | 6.1 OpenFPGA Flow                                                                                                                                                                                        | 55<br>55<br>59                               |

| 7 | 7.1General Hierarchy67.2Additional Syntax to Original VPR XML67.3Configuration Protocol77.4Inter-Tile Direct Interconnection extensions87.5Simulation settings87.6Technology library97.7Circuit Library9 | 57<br>57<br>58<br>72<br>32<br>34<br>91<br>93 |

|   | 7.8 Circuit model examples                                                                                                                                                                               | 1.                                           |

|    | 7.9       Bind circuit modules to VPR architecture         7.10       Fabric Key             |                   |

|----|----------------------------------------------------------------------------------------------|-------------------|

| 8  | OpenFPGA Shell         8.1       Launch OpenFPGA Shell                                       | <b>149</b><br>149 |

|    | 8.2 OpenFPGA Script Format                                                                   |                   |

|    | 8.3 Commands                                                                                 |                   |

| 9  | FPGA-SPICE                                                                                   | 177               |

|    | O.1    Command-line Options                                                                  |                   |

|    | 9.2    Hierarchy of SPICE Output Files                                                       |                   |

|    | 9.3 Run SPICE simulation                                                                     |                   |

|    | 9.4   Create Customized SPICE Modules                                                        | 180               |

| 10 | FPGA-Verilog                                                                                 | 181               |

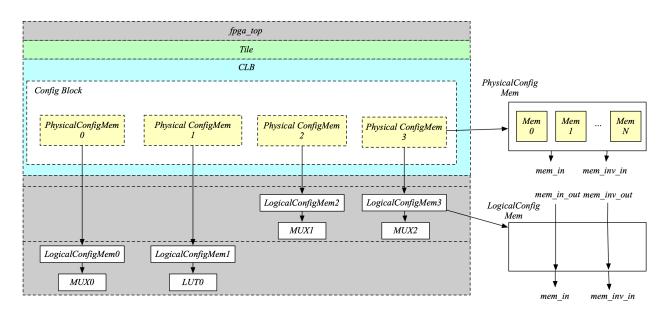

|    | 10.1 Fabric Netlists                                                                         | 181               |

|    | 10.2 Testbench                                                                               | 185               |

|    | 10.3 Mock FPGA Wrapper                                                                       | 186               |

| 11 | FPGA-Bitstream                                                                               | 189               |

|    | 11.1 Generic Bitstream                                                                       |                   |

|    | 11.2 Fabric-dependent Bitstream                                                              |                   |

| 10 |                                                                                              | 101               |

| 12 | File Formats          12.1       Pin Constraints File (.xml)                                 | <b>191</b>        |

|    | 12.1       Fill Constraints File (.xml)         12.2       Repack Design Constraints (.xml)  |                   |

|    | 12.2       Repack Design Constraints (XIII)         12.3       Architecture Bitstream (XIII) |                   |

|    | 12.4       Fabric-dependent Bitstream                                                        |                   |

|    | 12.5   Bitstream Setting (.xml)                                                              |                   |

|    | 12.6 Fabric Key (.xml)                                                                       |                   |

|    |                                                                                              | 207               |

|    | 12.8 I/O Information File (.xml)                                                             |                   |

|    |                                                                                              | 209               |

|    | 12.10 Bus Group File (.xml)                                                                  |                   |

|    | 12.11 Pin Constraints File (.pcf)                                                            |                   |

|    | 12.12 Pin Table File (.csv)                                                                  |                   |

|    | 12.13 Clock Network (.xml)                                                                   |                   |

|    | 12.14 Fabric I/O Naming (.xml)       12.15 Fabric Module Naming (.xml)                       |                   |

|    | 12.15 Fabric Module Naming ()         12.16 Tile Organization (.xml)                         |                   |

|    | 12.17 Fabric Pin Physical Location File (.xml)                                               |                   |

| 10 |                                                                                              |                   |

| 13 |                                                                                              | 223               |

|    | 13.1       Fabric Key Assistant         13.2       Module Rename Assistant                   | 223               |

|    |                                                                                              | 224               |

| 14 | Version Number                                                                               | 227               |

|    | 14.1 Convention                                                                              | 227               |

|    | 14.2 Version Update Rules                                                                    | 227               |

| 15 | Backward compatibility                                                                       | 229               |

|    |                                                                                              | 229               |

| 17 | *                                                                                            | 174               |

| 16 |                                                                                              | <b>231</b> 232    |

|    |                                                                                              | 252               |

|     | 16.2 Release Docker Images       |     |

|-----|----------------------------------|-----|

|     | 16.3 CI after cloning repository | 232 |

| 17  | Regression Tests                 | 233 |

|     | 17.1 Run a Test                  |     |

|     | 17.2 Test Options                | 233 |

| 18  | Tcl API                          | 235 |

| 19  | Contact                          | 237 |

| 20  | Acknowledgement                  | 239 |

| 21  | Publications & References        | 241 |

| 22  | Indices and tables               | 243 |

| Bil | bliography                       | 245 |

| Inc | lex                              | 247 |

### CHAPTER

# WHY OPENFPGA?

Note: If this is your first time learning OpenFPGA, we strongly recommend you to watch the introduction video

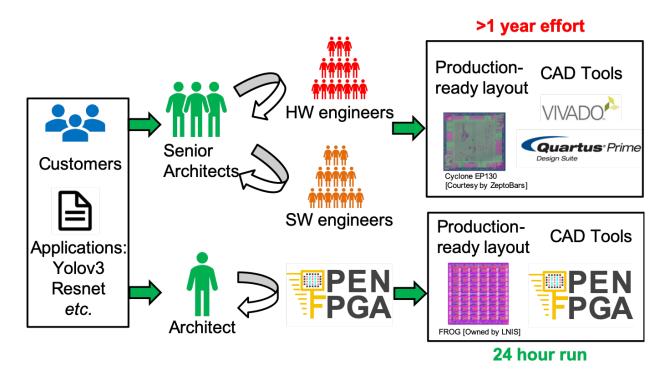

OpenFPGA aims to be an open-source framework that enables rapid prototyping of customizable FPGA architectures. As shown in Fig. 1.1, a conventional approach will take a large group of experienced engineers more than one year to achieve production-ready layout and associated CAD tools. In fact, most of the engineering efforts are spent on manual layouts and developing ad-hoc CAD support.

Fig. 1.1: Comparison on engineering time and effort to prototype an FPGA using OpenFPGA and conventional approaches [All the layout figures are publishable under the proper licenses]

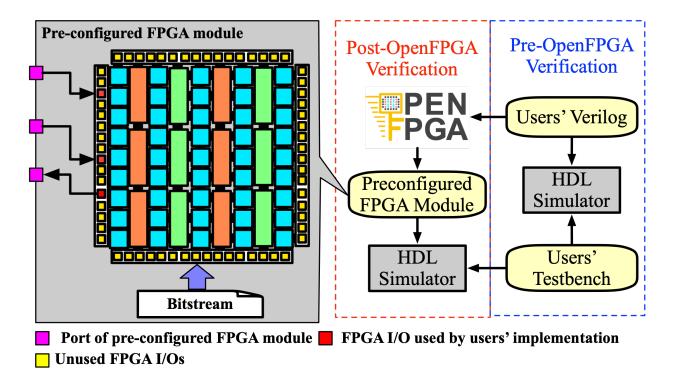

Using OpenFPGA, the development cycle in both hardware and software can be significantly accelerated. OpenFPGA can automatically generate Verilog netlists describing a full FPGA fabric based on an XML-based description file. Thanks to modern semi-custom design tools, production-ready layout generation can be achieved within 24 hours. To help sign-off, OpenFPGA can auto-generate Verilog testbenches to validate the correctness of FPGA fabric using modern verification tools. OpenFPGA also provides native bitstream generation support based on the same XML-based

description file used in Verilog generation, avoiding the recurring engineering in developing CAD tools for different FPGAs. Once the FPGA architecture is finalized, the CAD tool is ready to use.

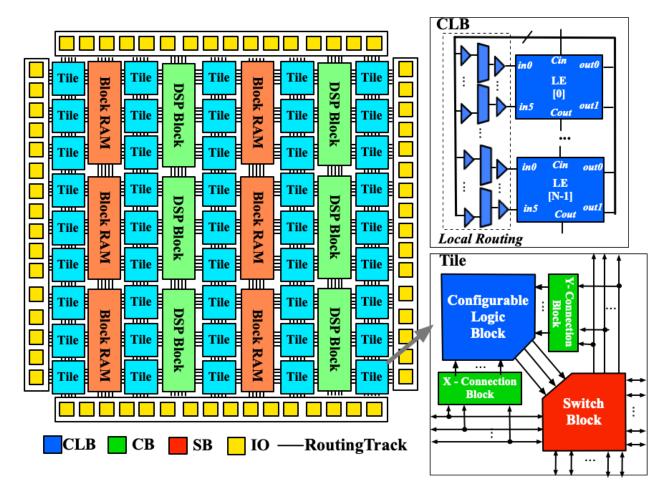

OpenFPGA can support any architecture that VPR can describe, covering most of the architecture enhancements available in modern FPGAs, and hence unlocks a large design space in prototyping customizable FPGAs. In addition, OpenFPGA provides enriched syntax which allows users to customize primitive circuits designed down to transistorlevel parameters. This helps developers to customize the P.P.A. (Power, Performance and Area) to the best. All these features open the door of prototyping/studying flexible FPGAs to a small group of junior engineers or researchers.

In terms of tool functionality, OpenFPGA consists of the following parts: FPGA-Verilog, FPGA-SDC, FPGA-Bitstream and FPGA-SPICE. The rest of this section will focus on detailed motivation for each of them, as depicted in Fig. 1.2.

Fig. 1.2: OpenFPGA: a unified framework for chip designer and FPGA programmer

# **1.1 Fully Customizable Architecture**

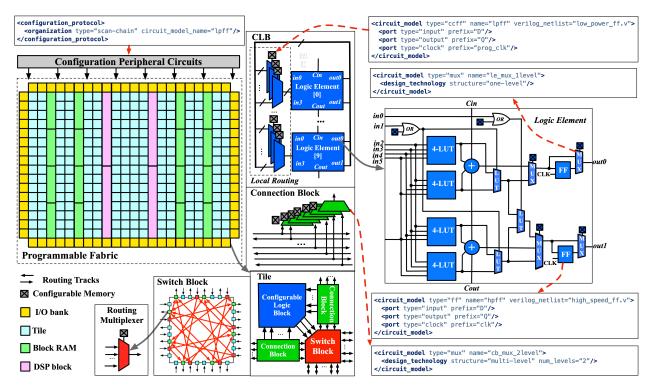

OpenFPGA supports VPR's architecture description language, which allows users to define versatile programmable fabrics down to point-to-point interconnection. OpenFPGA leverages VPR's architecture description by introducing an XML-based architecture annotation, enabling fully customizable FPGA fabric down to circuit elements. As illustrated in *OpenFPGA architecture description language enabling fully customizable FPGA architecture and circuit-level implementation*, OpenFPGA's architecture annotation covers a complete FPGA fabric, including both the programmable fabric and the configuration peripheral.

Fig. 1.3: OpenFPGA architecture description language enabling fully customizable FPGA architecture and circuit-level implementation

The technical details can be found in our papers [TGMG19] [TGA+19].

# 1.2 FPGA-Verilog

Driven by the strong need in data processing applications, Field Programmable Gate Arrays (FPGAs) are playing an ever-increasing role as programmable accelerators in modern computing systems. To fully unlock processing capabilities for domain-specific applications, FPGA architectures have to be tailored for seamless cooperation with other computing resources. However, prototyping and bringing to production a customized FPGA is a costly and complex endeavor even for industrial vendors.

OpenFPGA, an opensource framework, aims to rapidly prototype customizable FPGA architectures through a semicustom design approach. We propose an XML-to-Prototype design flow, where the Verilog netlists of a full FPGA fabric can be autogenerated using an extension of the XML language from the VTR framework and then fed into a back-end flow to generate production-ready layouts. FPGA-Verilog is designed to output flexible and standard Verilog netlists, enabling various backend choices, as illustrated in *FPGA-Verilog enabling flexible backend flows*.

Fig. 1.4: FPGA-Verilog enabling flexible backend flows

The technical details can be found in our papers [TGC+20] [TGG+20] [GTG21]

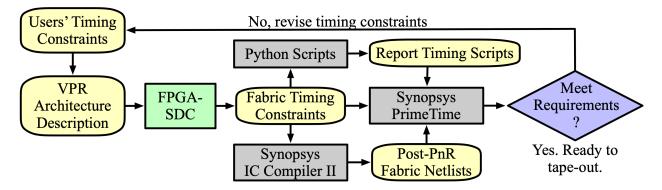

# 1.3 FPGA-SDC

Design constraints are indepensible in modern ASIC design flows to guarantee the performance level. OpenFPGA includes a rich SDC generator in the OpenFPGA framework to deal with both PnR constraints and sign-off timing analysis. Our flow automatically generates two sets of SDC files.

- The first set of SDC is designed for the P&R flow, where all the combinational loops are broken to enable well controlled timing-driven P&R. In addition, there are SDC files devoted to constrain pin-to-pin timing for all the resources in FPGAs, in order to obtain nicely constrained and homogeneous delays across the fabric. OpenFPGA allows users to define timing constraints in the architecture description and outputs timing constraints in standard format, enabling fully timing constrained backend flow (see *FPGA-SDC enabling iterative timing constrained backend flow*).

- The second set of SDC is designed for the timing analysis of a benchmark at the post P&R stage.

Fig. 1.5: FPGA-SDC enabling iterative timing constrained backend flow

The technical details can be found in our papers [TGA+19] [TGC+20] [TGG+20].

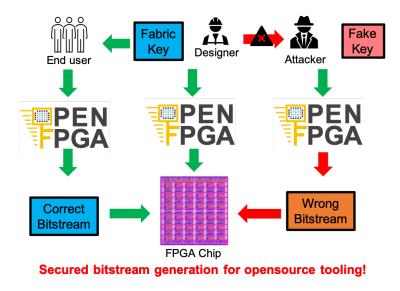

# 1.4 FPGA-Bitstream

EDA support is essential for end-users to implement designs on a customized FPGA. OpenFPGA provides a generalpurpose bitstream generator FPGA-Bitstream for any architecture that can be described by VPR. As the native CAD tool for any customized FPGA that is produced by FPGA-Verilog, FPGA-Bitstream is ready to use once users finalize the XML-based architecture description file. This eliminates the huge engineering efforts spent on developing bitstream generators for customized FPGAs. Using FPGA-Bitstream, users can launch (1) Verilog-to-Bitstream flow, the typical implementation flow for end-users; (2) Verilog-to-Verification flow. OpenFPGA can output Verilog testbenches with self-testing features to validate users' implementations on their customized FPGA fabrics.

The technical details can be found in our papers [TGMG19] [TGA+19].

# 1.5 FPGA-SPICE

The built-in timing and power analysis engines of VPR are based on analytical models [BRM99, GW12]. Analytical model-based analysis can promise accuracy only on a limited number of circuit designs for which the model is valid. As the technology advancements create more opportunities on circuit designs and FPGA architectures, the analytical power model requires updates to follow the new trends. However, without referring to simulation results, the analytical power models cannot prove their accuracy. SPICE simulators have the advantages of generality and accuracy over analytical models. For this reason, SPICE simulation results are often selected to check the accuracy of analytical models. Therefore, there is a strong need for a simulation-based power analysis approach for FPGAs, which can support general circuit designs.

It motivates us to develop FPGA-SPICE, an add-on for the current State-of-Art FPGA architecture exploration tools, VPR [RLY+12]. FPGA-SPICE aims at generating SPICE netlists and testbenches for the FPGA architectures supported by VPR. The SPICE netlists and testbenches are generated according to the placement and routing results of VPR. As a result, SPICE simulator can be used to perform precise delay and power analysis. The SPICE simulation results are useful in three aspects: (1) they provide accurate power analysis; (2) they help to improve the accuracy of built-in analytical models; and moreover (3) they create opportunities in developing novel analytical models.

SPICE modeling for FPGA architectures requires detailed transistor-level modeling for all the circuit elements within the considered FPGA architecture. However, current VPR architectural description language [LAR11] does not offer enough transistor-level parameters to model the most common circuit modules, such as multiplexers and LUTs. Therefore, we are developing an extension on the VPR architectural description language to model the transistor-level circuit designs.

The technical details can be found in our papers [TGM15] [TGMG19].

### CHAPTER

TWO

# **TECHNICAL HIGHLIGHTS**

The following lists of technical features were created to help users find their needs for customizing FPGA fabrics.(as of February 2021)

# 2.1 Supported Circuit Designs

| Circuit Types          | Auto-<br>generation | User-<br>Defined | Design Topologies                                                                                                                                                                                                                                                               |

|------------------------|---------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

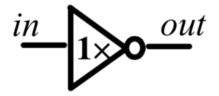

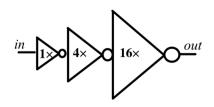

| Inverter               | Yes                 | Yes              | <ul> <li>Power-gated In-<br/>verter 1x example</li> <li>Inverter 1x Example</li> <li>Tapered inverter<br/>16x example</li> </ul>                                                                                                                                                |

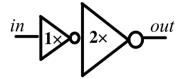

| Buffer                 | Yes                 | Yes              | <ul> <li>Buffer 2x example</li> <li>Power-gated Buffer<br/>4x example</li> <li>Tapered buffer 64x<br/>example</li> </ul>                                                                                                                                                        |

| AND gate               | Yes                 | Yes              | • 2-input AND Gate                                                                                                                                                                                                                                                              |

| OR gate                | Yes                 | Yes              | • 2-input OR Gate                                                                                                                                                                                                                                                               |

| MUX2 gate              | Yes                 | Yes              | • MUX2 Gate                                                                                                                                                                                                                                                                     |

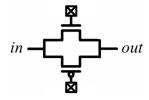

| Pass gate              | Yes                 | Yes              | <ul> <li>Transmission-gate<br/>Example</li> <li>Pass-transistor Ex-<br/>ample</li> </ul>                                                                                                                                                                                        |

| Look-Up Table          | Yes                 | Yes              | <ul> <li>Any size</li> <li>Single-Output LUT</li> <li>Standard Frac-<br/>turable LUT</li> <li>LUT with Harden<br/>Logic</li> </ul>                                                                                                                                              |

| Routing<br>Multiplexer | Yes                 | No               | <ul> <li>Any size</li> <li>Multi-level Multi-<br/>plexer</li> <li>One-level Multi-<br/>plexer</li> <li>Tree-like Multi-<br/>plexer</li> <li>Standard Cell Mul-<br/>tiplexer</li> <li>Multiplexer with<br/>Local Encoder</li> <li>Multiplexer with<br/>Constant Input</li> </ul> |

| 2.1. Supported Circ    | cuit Designs        |                  | Constant Inpat                                                                                                                                                                                                                                                                  |

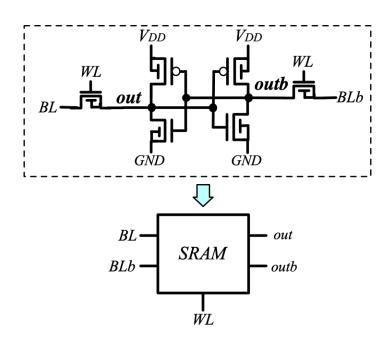

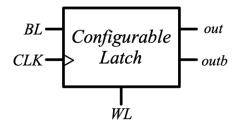

| Configurable           | No                  | Yes              | <ul> <li>Configurable Latch</li> <li>SRAM with BL/WL</li> <li>Regular</li> </ul>                                                                                                                                                                                                |

• The user defined netlist could come from a standard cell. See *Build an FPGA fabric using Standard Cell Libraries* for details.

# 2.2 Supported FPGA Architectures

We support most FPGA architectures that VPR can support! The following are the most commonly seen architectural features:

| Block Type             | Architecture features                                                                                                                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Programmable Block     | <ul> <li>Single-mode Configurable Logic Block (CLB)</li> <li>Multi-mode Configurable Logic Block (CLB)</li> <li>Single-mode heterogeneous blocks</li> <li>Multi-mode heterogeneous blocks</li> <li>Flexible local routing architecture</li> </ul> |

| Routing Block          | <ul> <li>Tileable routing architecture</li> <li>Flexible connectivity</li> <li>Flexible Switch Block Patterns</li> </ul>                                                                                                                          |

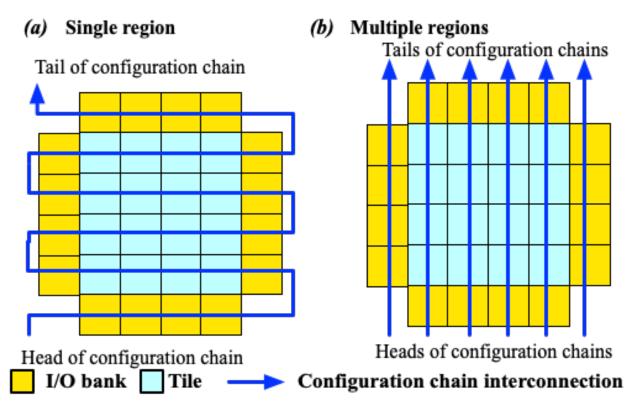

| Configuration Protocol | <ul> <li>Chain-based organization</li> <li>Frame-based organization</li> <li>Memory bank organization</li> <li>Flatten organization</li> </ul>                                                                                                    |

# 2.3 Supported Verilog Modeling

OpenFPGA supports the following Verilog features in auto-generated netlists for circuit designs

- Synthesizable Behavioral Verilog

- Structural Verilog

- Implicit/Explicit port mapping

### CHAPTER

### THREE

### **GETTING STARTED**

### 3.1 How to Compile

Note: We recommend you to watch a tutorial video about how-to-compile before getting started

### 3.1.1 Supported Operating Systems

OpenFPGA is continously tested with Ubuntu 20.04 and partially on Ubuntu 22.04 It might work with earlier versions and other distributions.

In addition to continous integration, our community users have tested OpenFPGA on their local machines using the following operating systems:

- CentOS 7.8

- CentOS 8

- Ubuntu 18.04

- Ubuntu 21.04

- Ubuntu 22.04

### 3.1.2 Build Steps

OpenFPGA uses CMake to generate the Makefile scripts. In general, please follow the steps to compile

```

git clone https://github.com/LNIS-Projects/OpenFPGA.git

cd OpenFPGA

make all

```

**Note:** OpenFPGA requires gcc/g++ version > 7 and clang version > 6.

Note: cmake3.12+ is recommended to compile OpenFPGA with GUI

Note: Recommend using make -j<int> to accelerate the compilation, where <int> denotes the number of cores to be used in compilation.

Note: VPR's GUI requires gtk-3, and can be enabled with make .. CMAKE\_FLAGS="-DVPR\_USE\_EZGL=on"

#### **Quick Compilation Verification**

Note: Ensure that you install python dependencies in *Dependencies*.

To quickly verify the tool is well compiled, users can run the following command from OpenFPGA root repository

### 3.1.3 Build Options

General build targets are available in the top-level makefile. Call help desk to see details

make help

The following options are available for a custom build

#### BUILD\_TYPE=<string>

Specify the type of build. Can be either release or debug. By default, release mode is selected (full optimization on runtime)

#### CMAKE\_FLAGS=<string>

Force build flags to CMake. The following flags are available

- DOPENFPGA\_WITH\_TEST=[ON|OFF]: Enable/Disable the test build

- DOPENFPGA\_WITH\_YOSYS=[ON|OFF]: Enable/Disable the build of yosys. Note that when disabled, the build of yosys-plugin is also disabled

- DOPENFPGA\_WITH\_YOSYS\_PLUGIN=[ON|OFF]: Enable/Disable the build of yosys-plugin.

- DOPENFPGA\_WITH\_VERSION=[ON|OFF]: Enable/Disable the build of version number. When disabled, version number will be displayed as an empty string.

- DOPENFPGA\_WITH\_SWIG=[ON|OFF]: Enable/Disable the build of SWIG, which is required for integrating to high-level interface.

- OPENFPGA\_ENABLE\_STRICT\_COMPILE=[ON|OFF]: Specifies whether compiler warnings should be treated as errors (e.g. -Werror)

**Warning:** By default, only required modules in *Verilog-to-Routing* (VTR) is enabled. On other words, abc, odin, yosys and other add-ons inside VTR are not built. If you want to enable them, please look into the dedicated options of CMake scripts.

#### CMAKE\_GOALS=<string>

Specify the build target for CMake system. For example, cmake\_goals=openfpga indicates that only openfpga binary will be compiled. For a detailed list of targets, use make list\_cmake\_targets to show. By default, all the build targets will be included.

### 3.1.4 Dependencies

Dependencies can be installed upon the use of OpenFPGA on different systems In general, OpenFPGA requires specific versions for the following dependencies:

#### cmake

version >3.12 for graphical interface

#### iverilog

version 10.3+ is required to run Verilog-to-Verification flow

#### **Ubuntu 20.04**

· Dependencies required to build the code base

```

#!/usr/bin/env bash

# The package list is designed for Ubuntu 20.04 LTS

add-apt-repository -y ppa:ubuntu-toolchain-r/test

apt-get update

apt-get install -y \

autoconf \

automake \

bison \setminus

ccache \setminus

cmake ∖

ctags \

curl \

doxygen \

flex \

fontconfig \

gdb ∖

git \

gperf \

iverilog \

libc6-dev ∖

libcairo2-dev ∖

libevent-dev ∖

libffi-dev \

libfontconfig1-dev \

liblist-moreutils-perl \

libncurses5-dev \

libreadline-dev \

libreadline8 \

libx11-dev ∖

libxft-dev ∖

libxml++2.6-dev \

make \

```

| perl \                         |

|--------------------------------|

| pkg-config $\setminus$         |

| python3 \                      |

| python3-setuptools $\setminus$ |

| python3-lxml $\setminus$       |

| python3-pip \                  |

| qt5-default \                  |

| tcllib \                       |

| tcl8.6-dev ∖                   |

| texinfo \                      |

| time \                         |

| valgrind $\setminus$           |

| wget \                         |

| zip \                          |

| swig \                         |

| expect \                       |

| g++−7 ∖                        |

| gcc-7 \                        |

| g++-8 \                        |

| gcc-8 \                        |

| g++-9 ∖                        |

| gcc-9 \                        |

| g++-10 ∖                       |

| $gcc-10 \setminus$             |

| g++-11 ∖                       |

| gcc-11 $\setminus$             |

| clang-6.0 \                    |

| clang-7 \                      |

| clang-8 \                      |

| $clang-10 \setminus$           |

| clang-format-10 $\setminus$    |

| libxml2-utils \                |

| libssl-dev                     |

• Dependencies required to run regression tests

```

# Update as required by some packages

apt-get update

apt-get install --no-install-recommends -y \

libdatetime-perl libc6 libffi-dev libgcc1 libreadline8 libstdc++6 \

libtcl8.6 tcl python3.8 python3-pip zlib1g libbz2-1.0 \

iverilog git rsync make curl wget tree python3.8-venv

```

Note: Python packages are also required

```

python3 -m pip install -r requirements.txt

```

• Dependencies required to build documentation

#!/usr/bin/env bash

```

# The package list is designed for Ubuntu 20.04 LTS

apt-get install python3-sphinx

python3 -m pip install -r docs/requirements.txt

```

#### Ubuntu 22.04

#!/usr/bin/env bash

• Dependencies required to build the code base

```

# The package list is designed for Ubuntu 20.04 LTS

add-apt-repository -y ppa:ubuntu-toolchain-r/test

apt-get update

apt-get install -y \

autoconf \

automake \

bison ∖

ccache \

cmake ∖

exuberant-ctags \setminus

curl \

doxygen \

flex \

fontconfig \

gdb ∖

git ∖

gperf \

iverilog \

libc6-dev ∖

libcairo2-dev ∖

libevent-dev \setminus

libffi-dev ∖

libfontconfig1-dev \

liblist-moreutils-perl \

libncurses5-dev \

libreadline-dev \setminus

libreadline8 \

libx11-dev ∖

libxft-dev ∖

libxml++2.6-dev \setminus

make \

perl \

pkg-config \setminus

python3 \

python3-setuptools \setminus

python3-lxml \

python3-pip \

qtbase5-dev ∖

tcllib ∖

tcl8.6-dev ∖

texinfo \

```

| \ |

|---|

|   |

|   |

• Dependencies required to run regression tests

```

# Update as required by some packages

apt-get update

apt-get install --no-install-recommends -y \

libdatetime-perl libc6 libffi-dev libgcc1 libreadline8 libstdc++6 \

libtcl8.6 tcl python3.8 python3-pip zlib1g libbz2-1.0 \

iverilog git rsync make curl wget tree python3.8-venv

```

Note: Python packages are also required

python3 -m pip install -r requirements.txt

• Dependencies required to build documentation

#!/usr/bin/env bash

```

# The package list is designed for Ubuntu 20.04 LTS

apt-get install python3-sphinx

python3 -m pip install -r docs/requirements.txt

```

### 3.1.5 Running with pre-built docker image

Users can skip the traditional installation process by using the Dockerized version of the OpenFPGA tool. The OpenFPGA project maintains the docker image/Github package of the latest stable version of OpenFPGA in the following repository openfpga-master. This image contains precompiled OpenFPGA binaries with all prerequisites installed.

```

# To get the docker image from the repository,

docker pull ghcr.io/lnis-uofu/openfpga-master:latest

# To invoke openfpga_shell

docker run -it ghcr.io/lnis-uofu/openfpga-master:latest openfpga/openfpga bash

```

# 3.2 OpenFPGA Shell Commands

OpenFPGA provides *bash/zsh* shell-based shortcuts to perform all essential functions and navigate through the directories. Go to the OpenFPGA directory and source openfpga.sh,

```

export OPENFPGA_PATH=<path-to-openfpga-repository-root>

cd ${OPENFPGA_PATH} && source openfpga.sh

```

Note: The OpenFPGA shortcut works with only a bash-like shell. e.g., bash/zsh/fish, etc.

### 3.2.1 Commands

Once the openfpga.sh script is sourced, you can run any following commands directly in the terminal.

#### list-tasks

This command lists all the OpenFPGA tasks from the current task directory. default task directory is considered as  ${OPENFPGA_PATH}/openfpga_flow/tasks$

#### run-task <task\_name> \*\*kwarags

This command runs the specified task. The script will first look for the task in the current working directory. If it is not in the current directory, it will then search in TASK\_DIRECTORY (relative to task directory). You can also provide a path as a task\_name, for example, run-task basic\_tests/generate\_fabric The valid arguments listed here <\_openfpga\_task\_args>`\_, you can also run *run-task run-task* to get the list of command-line arguments.

#### create-task <task\_name> <template>

It creates a template task in the current directory with the given task\_name. the template is an optional argument; there are two templates currently configured - vpr\_blif: A template task for running flow with *.blif* file as an input (VPR + Netlist generation) - yosys\_vpr: A template task for running flow with *.v* file as an input (Synthesis + VPR + Netlist generation) you can also use this command to copy any example project; use a list-tasks command to get the list of example projects for example create-task \_my\_task\_copy basic\_tests/generate\_fabric create a copy of the basic\_tests/generate\_fabric task in the current directory with \_my\_task\_copy name.

#### goto\_task <task\_name> <run\_num[default 0]>

This command navigate shell to specific run-directory of the given task. For example *goto\_task lab1* 2 will change directory to *run002* runt directory of *lab2*

#### clear-task-run <task\_name>

Clears all run directories of the given task

#### run-modelsim <task\_name>

This command runs the verification using ModelSim. The test benches are generated during the OpenFPGA run. **Note**: users need to have VSIM installed and configured

#### run-regression-local

This script runs the regression test locally using the current version of OpenFPGA. **NOTE** Important before making a pull request to the master

#### unset-openfpga

Unregisters all the shortcuts and commands from the current shell session

# 3.3 Supported Tools

### 3.3.1 Internal Tools

To enable various design purposes, OpenFPGA integrates several tools to i.e., FPGA-Verilog, FPGA-SDC and FPGAbitstream (highlighted green in *OpenFPGA tool suites and design flows*, with other popular open-source EDA tools, i.e., VPR and Yosys.

Fig. 3.1: OpenFPGA tool suites and design flows

### 3.3.2 Third-Party Tools

OpenFPGA accepts and outputs in standard file formats, and therefore can interface a wide range of commercial and open-source tools.

| Usage   | Tools                   | Version Requirement |

|---------|-------------------------|---------------------|

| Back-   | Synopsys IC Compiler II | v2019.03 or later   |

| end     | Cadence Innovus         | v19.1 or later      |

| Timing  | Synopsys PrimeTime      | v2019.03 or later   |

| Ana-    | Cadence Tempus          | v19.15 or later     |

| lyzer   |                         |                     |

| Verifi- | Synopsys VCS            | v2019.06 or later   |

| cation  | Synopsys Formality      | v2019.03 or later   |

|         | Mentor ModelSim         | v10.6 or later      |

|         | Mentor QuestaSim        | v2019.3 or later    |

|         | Cadence NCSim           | v15.2 or later      |

|         | Icarus iVerilog         | v10.1 or later      |

• The version requirements is based on our local tests. Older versions may work.

### CHAPTER

FOUR

# **DESIGN FLOWS**

# 4.1 Generate Fabric Netlists

Note: You may watch the video representation of this tutorial

#### This tutorial will show an example how to

· generate Verilog netlists for a FPGA fabric

**Note:** Before running any design flows, please checkout the tutorial *How to Compile*, to ensure that you have an operating copy of OpenFPGA installed on your computer.

### 4.1.1 Prepare Task Configuration File

OpenFPGA provides push-button scripts for users to run design flows (see details in *OpenFPGA Task*). Users can customize their flow-run by crafting a task configuration file.

Here, we consider an existing test case generate\_fabric. In the task configuration file, you can specify the XMLbased architecture files in LINE 21 and LINE 25 that describe the architecture of the FPGA fabric. In this example, we are using a low-cost FPGA architecture similar to the lattice ICE40 series

Also, in LINE 20, you can specify the openfpga shell script to be executed. Here, we are using an example script which is golden reference to generate Verilog netlists

Note: You can use text editor to customize the configuration file. Here, we use it as is.

### 4.1.2 Run OpenFPGA Task

After finalizing your configuration file, you can run the task by calling the python script with the given path to task configuration file.

python3 openfpga\_flow/scripts/run\_fpga\_task.py basic\_tests/generate\_fabric

When the flow run is executed, you can visit the runtime directory and check the Verilog netlists.

Note that your task-run outcomes are stored in the directory called latest in the same level of your task configuration file.

The Verilog netlists are generated in the following directory

Note: \${OPENFPGA\_PATH} is the root directory of OpenFPGA

Note: See Fabric Netlists for the netlist details.

In the Verilog files, you can validate if the Verilog description is consistent as your definition in the architecture file. The Verilog files can be then used to drive different tools, such as layout generation *etc*.

### 4.1.3 Run icarus iVerilog Compilation

Go to the directory

Compile with iVerilog command:

iverilog SRC/fabric\_netlists.v

Note: Please ensure that iVerilog is installed correctly on your computer

If compilation is successful, you can see a file a.out in the directory.

# 4.2 From Verilog to Verification

This tutorial will show an example how to

- generate Verilog netlists for a FPGA fabric

- generate Verilog testbenches for a RTL design

- run HDL simulation to verify the functional correctness of the implemented FPGA fabric

**Note:** Before running any design flows, please checkout the tutorial *How to Compile*, to ensure that you have an operating copy of OpenFPGA installed on your computer.

### 4.2.1 Netlist Generation

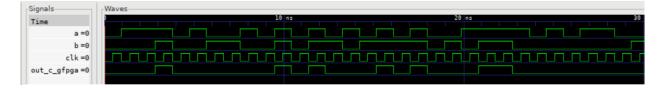

We will use the openfpga\_flow scripts (see details in *OpenFPGA Task*) to generate the Verilog netlists and testbenches. Here, we consider a representative but fairly simple FPGA architecture, which is based on 4-input LUTs. We will map a 2-input AND gate to the FPGA fabric, and run a full testbench (see details in *Testbench*)

We will simply execute the following openfpga task-run by

Detailed settings, such as architecture XML files and RTL designs, can be found at  ${OPENFPGA_PATH}/ openfpga_flow/tasks/basic_tests/full_testbench/configuration_chain/config/task.conf.$

**Note:** \${OPENFPGA\_PATH} is the root directory of OpenFPGA

After this task-run, you can find all the generated netlists and testbenches at

Note: See Fabric Netlists and Testbench for the netlist details.

#### 4.2.2 Run icarus iVerilog Simulation

#### **Through OpenFPGA Scripts**

By default, the configuration\_chain task-run will execute iVerilog simulation automatically. The simulation results are logged in

If the verification passed, you should be able to see Simulation Succeed in the log file.

All the waveforms are stored in the and2\_formal.vcd file. To visualize the waveforms, you can use the GTKWave.

#### **Manual Method**

If you want to run iVerilog simulation manually, you can follow these steps:

source iverilog\_output.txt

vvp compiled\_and2

### **Debugging Tips**

If you want to apply full visibility to the signals, you need to change the following line in

from

\$dumpvars (1, and2\_autocheck\_top\_tb);

to

```

$dumpvars (12, and2_autocheck_top_tb);

```

### 4.2.3 Run Modelsim Simulation

Alternatively, you can run Modelsim simulations through openfpga\_flow scripts or manually.

Note: Before starting, please ensure that Mentor Modelsim has been correctly installed on your local environment.

#### Through OpenFPGA Scripts

You can simply call the python script in the following line:

The script will automatically create a Modelsim project at

```

${OPENFPGA_PATH}/openfpga_flow/tasks/basic_tests/full_testbench/configuration_chain/

$$\overline$$\k4_N4_tileable_40nm/and2/MIN_ROUTE_CHAN_WIDTH/MSIM2/$$$$

```

and run the simulation.

You may open the project and visualize the simulation results.

#### **Manual Method**

Modify the fpga\_defines.v (see details in *Fabric Netlists*) at

by **deleting** the line

define ICARUS\_SIMULATOR 1

Create a folder MSIM under

Under the MSIM folder, create symbolic links to SRC folder and reference benchmarks by

ln -s ../SRC ./

ln -s ../and2\_output\_verilog.v ./

Note: Depending on the operating system, you may use other ways to create the symbolic links

Launch ModelSim under the MSIM folder and create a project by following Modelsim user manuals.

Add the following file to your project:

Compile the netlists, create a simulation configuration and specify and2\_autocheck\_top\_tb at the top unit.

Execute simulation with run -all You should see Simulation Succeed in the output log.

### 4.3 From Verilog to GDSII

The generated Verilog code can be used through a semi-custom design flow to generate the layout.

Because of the commercial nature of the semi-custom design tools we are using, we cannot share the different scripts that we are using. However, we can show the results to serve as a proof-of-concept and encourage research through it.

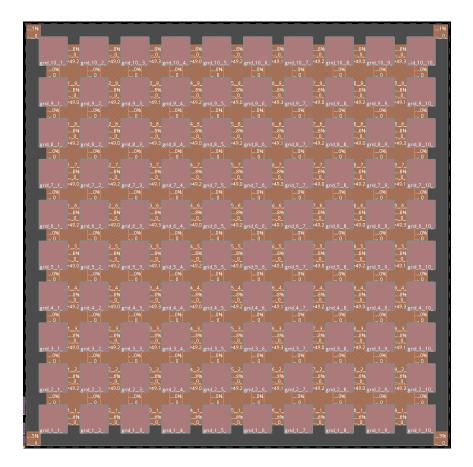

Layout\_Diagram shows the different steps involved in realizing the layout for any design. CTS stands for Clock Tree Synthesis, and PPA stands for Power-Performance-Area. First, we create the floorplan with the different tiles involved in the FPGA, i.e., the CLBs and place them. Then the clock tree is generated. Finally, the design is routed, and the PPA signoff is realized. Coupled with FPGA-SPICE, we get silicon level analysis on the design.

In Layout\_Floorplan, we show the result we get from the floorplanning we get through Cadence Innovus.

### CHAPTER

# **ARCHITECTURE MODELING**

# 5.1 A Quick Start

In this tutorial, we will consider a simple but representative FPGA architecture to show you how to

- Adapt a VPR architecture XML file to OpenFPGA acceptable format

- Create an OpenFPGA architecture XML file to customize the primitive circuits

- Create a simulation setting XML file to specify the simulation settings

Through this quick example, we will introduce the key steps to build your own FPGA based on a VPR architecture template.

Note: These tips are generic and fundamental to build any architecture file for OpenFPGA.

# 5.1.1 Adapt VPR Architecture

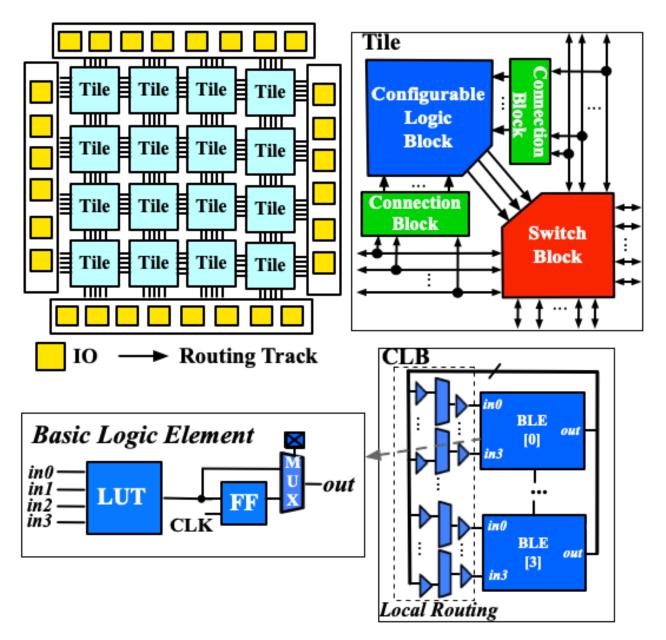

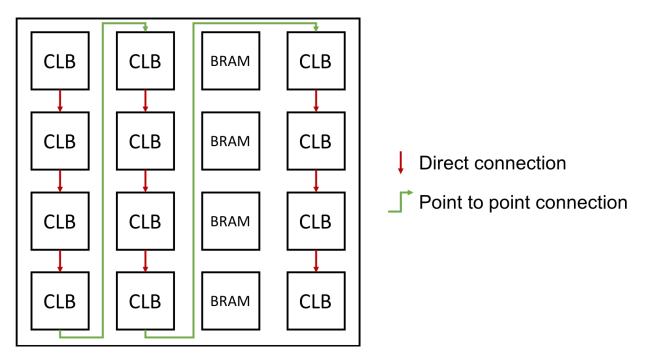

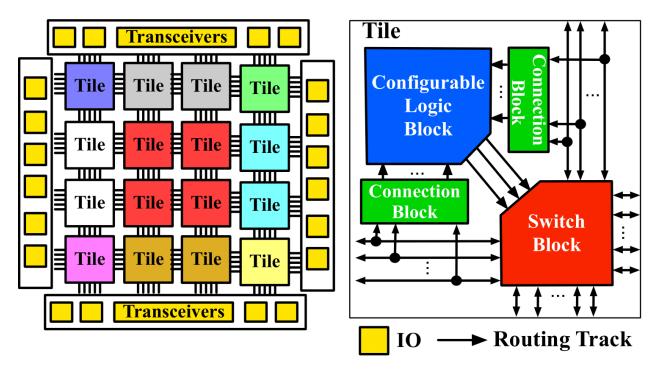

We start with the VPR architecture template. This file models a homogeneous FPGA, as illustrated in Fig. 5.1.

### A summary of the architectural features is as follows:

- An array of tiles surrounded by a ring of I/O blocks

- K4N4 Configurable Logic Block (CLB), which consists of four Basic Logic Elements (BLEs) and a fullyconnected crossbar. Each BLE contains a 4-input Look-Up Table (LUT), a Flip-Flop (FF) and a 2:1 routing multiplexer

- Length-1 routing wires interconnected by Wilton-Style Switch Block (SB)

The VPR architecture description is designed for EDA needs mainly, which lacks the details physical modeling required by OpenFPGA. Here, we show a step-by-step adaption on the architecture template.

Fig. 5.1: K4N4 FPGA architecture

#### Physical I/O Modeling

OpenFPGA requires a physical I/O block rather the abstract I/O modeling of VPR. The <pb\_type name="io"> under the <complexblocklist> should be adapted to the following:

```

<!-- Define I/O pads begin -->

<pb_type name="io">

<input name="outpad" num_pins="1"/>

<output name="inpad" num_pins="1"/>

<!-- A mode denotes the physical implementation of an I/O

This mode will not be used by packer but is mainly used for fabric verilog.

→generation

-->

<mode name="physical" packable="false">

<pb_type name="iopad" blif_model=".subckt io" num_pb="1">

<input name="outpad" num_pins="1"/>

<output name="inpad" num_pins="1"/>

</pb_type>

<interconnect>

<direct name="outpad" input="io.outpad" output="iopad.outpad">

<delay_constant max="1.394e-11" in_port="io.outpad" out_port="iopad.outpad"/>

</direct>

<direct name="inpad" input="iopad.inpad" output="io.inpad">

<delay_constant max="4.243e-11" in_port="iopad.inpad" out_port="io.inpad"/>

</direct>

</interconnect>

</mode>

<!-- Operating modes of I/O used by VPR

IOs can operate as either inputs or outputs. -->

<mode name="inpad">

<pb_type name="inpad" blif_model=".input" num_pb="1">

<output name="inpad" num_pins="1"/>

</pb_type>

<interconnect>

<direct name="inpad" input="inpad.inpad" output="io.inpad">

<delay_constant max="9.492000e-11" in_port="inpad.inpad" out_port="io.inpad"/>

</direct>

</interconnect>

</mode>

<mode name="outpad">

<pb_type name="outpad" blif_model=".output" num_pb="1">

<input name="outpad" num_pins="1"/>

</pb type>

<interconnect>

<direct name="outpad" input="io.outpad" output="outpad.outpad">

<delay_constant max="2.675000e-11" in_port="io.outpad" out_port="outpad.outpad"/</pre>

⇒>

</direct>

</interconnect>

</mode>

</pb_type>

```

Note that, there are several major changes in the above codes, when compared to the original code.

- We added a physical mode of I/O in addition to the original VPR I/O modeling, which is close to the physical implementation of an I/O cell. OpenFPGA will output fabric netlists base on the physical implementation rather than the operating modes.

- We remove the clock port of I/O is actually a dangling port.

- We specify that the phyical mode to be disabled for VPR packer by using packable=false. This can help reduce packer's runtime.

Since, we have added a new BLIF model subckt io to the architecture modeling, we should update the <models> XML node by adding a new I/O model.

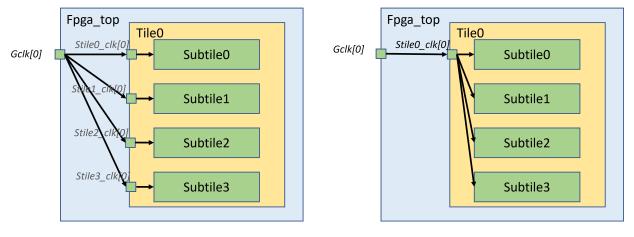

#### **Tileable Architecture**

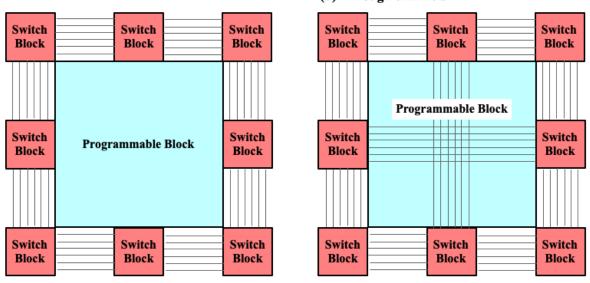

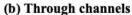

OpenFPGA does support fine-grained tile-based architecture as shown in Fig. 5.1. The tileable architecture leads to fast netlist generation as well as enables highly optimized physical designs through backend flow. To turn on the tileable architecture, the tileable property should be added to <layout> node.

<layout tileable="true">

By enabling this, all the Switch Blocks and Connection Blocks will be generated as identical as possible. As a result, for any FPGA array size, there are only 9 unique tiles to be generated in netlists. See details in [TGAG19].

Detailed guidelines can be found at Additional Syntax to Original VPR XML.

### 5.1.2 Craft OpenFPGA Architecture

OpenFPGA needs another XML file which contains detailed modeling on the physical design of FPGA architecture. This is designed to minimize the modification on the original VPR architecture file, so that it can be reused. You may create an XML file *k4\_n4\_openfpga\_arch.xml* and then add contents shown as follows.

#### **Overview on the Structure**

#### An OpenFPGA architecture including the following parts.

- Architecture modeling with a focus on circuit-level description

- Configuration protocol definition

- Annotation on the VPR architecture modules

These parts are organized as follows in the XML file.

```

<openfpga_architecture>

<!-- Technology-related (device/transistor-level) information

<technology_library>

</technology_library>

<!-- Circuit-level description -->

<circuit_library>

</circuit_library>

<!-- Configuration protocol definition -->

<configuration_protocol>

. . .

</configuration_protocol>

<!-- Annotation on VPR architecture modules -->

<connection_block>

</connection_block>

<switch_block>

. . .

</switch_block>

<routing_segment>

. . .

</routing_segment>

<pb_type_annotations>

. . .

</pb_type_annotations>

</openfpga_architecture>

```

#### Technology Library Definition

Technology information are all stored under the <technology\_library> node, which contains transistor-level information to build the FPGA. Here, we bind to the open-source ASU Predictive Technology Modeling (PTM) 45nm process library. See details in *Technology library*.

```

<design vdd="0.9" pn_ratio="2"/>

<pmos name="pch" chan_length="40e-9" min_width="140e-9" variation="logic_</pre>

→transistor_var"/>

<nmos name="nch" chan_length="40e-9" min_width="140e-9" variation="logic_</pre>

→transistor_var"/>

</device_model>

<device_model name="io" type="transistor">

<lib type="academia" ref="M" path="${OPENFPGA_PATH}/openfpga_flow/tech/PTM_45nm/</pre>

\rightarrow45nm.pm"/>

<design vdd="2.5" pn_ratio="3"/>

<pmos name="pch_25" chan_length="270e-9" min_width="320e-9" variation="io_</pre>

→transistor_var"/>

<nmos name="nch_25" chan_length="270e-9" min_width="320e-9" variation="io_</pre>

→transistor_var"/>

</device_model>

</device_library>

<variation_library>

<variation name="logic_transistor_var" abs_deviation="0.1" num_sigma="3"/>

<variation name="io_transistor_var" abs_deviation="0.1" num_sigma="3"/>

</variation_library>

</technology_library>

```

**Note:** These information are important for FPGA-SPICE to correctly generate netlists. If you are not using FPGA-SPICE, you may provide a dummy technology library.

### **Circuit Library Definition**

Circuit library is the crucial component of the architecture description, which contains a list of <circuit\_model>, each of which describes how a circuit is implemented for a FPGA component.

Typically, we will defined a few atom <circuit\_model> which are used to build primitive <circuit\_model>.

```

<circuit_library>

<!-- Atom circuit models begin-->

<circuit_model>

...

</circuit_model>

<!-- Atom circuit models end-->

<!-- Primitive circuit models begin -->

<circuit_model>

...

</circuit_model>

<!-- Primitive circuit models end -->

</circuit_library>

```

**Note:** Primitive <circuit\_model> are the circuits which are directly used to build a FPGA component, such as Look-Up Table (LUT). Atom <circuit\_model> are the circuits which are only used inside primitive <circuit\_model>.

In this tutorial, we need the following atom <circuit\_model>, which are inverters, buffers and pass-gate logics.

```

<!-- Atom circuit models begin-->

<circuit_model type="inv_buf" name="INVTX1" prefix="INVTX1" is_default="true">

<design_technology type="cmos" topology="inverter" size="1"/>

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<delay_matrix type="rise" in_port="in" out_port="out">

10e-12

</delay_matrix>

<delay_matrix type="fall" in_port="in" out_port="out">

10e-12

</delay_matrix>

</circuit_model>

<circuit_model type="inv_buf" name="buf4" prefix="buf4" is_default="false">

<design_technology type="cmos" topology="buffer" size="1" num_level="2" f_per_stage="4</pre>

→"/>

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<delay_matrix type="rise" in_port="in" out_port="out">

10e-12

</delay matrix>

<delay_matrix type="fall" in_port="in" out_port="out">

10e-12

</delay_matrix>

</circuit_model>

<circuit_model type="inv_buf" name="tap_buf4" prefix="tap_buf4" is_default="false">

<design_technology type="cmos" topology="buffer" size="1" num_level="3" f_per_stage="4</pre>

→"/>

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<delay_matrix type="rise" in_port="in" out_port="out">

10e-12

</delay matrix>

<delay_matrix type="fall" in_port="in" out_port="out">

10e-12

</delay_matrix>

</circuit_model>

<circuit_model type="pass_gate" name="TGATE" prefix="TGATE" is_default="true">

<design_technology type="cmos" topology="transmission_gate" nmos_size="1" pmos_size="2</pre>

→"/>

<input_buffer exist="false"/>

<output_buffer exist="false"/>

<port type="input" prefix="in" size="1"/>

<port type="input" prefix="sel" size="1"/>

<port type="input" prefix="selb" size="1"/>

<port type="output" prefix="out" size="1"/>

<delay_matrix type="rise" in_port="in sel selb" out_port="out">

10e-12 5e-12 5e-12

</delay_matrix>

<delay_matrix type="fall" in_port="in sel selb" out_port="out">

10e-12 5e-12 5e-12

</delay_matrix>

```

```

(continued from previous page)

```

```

</circuit model>

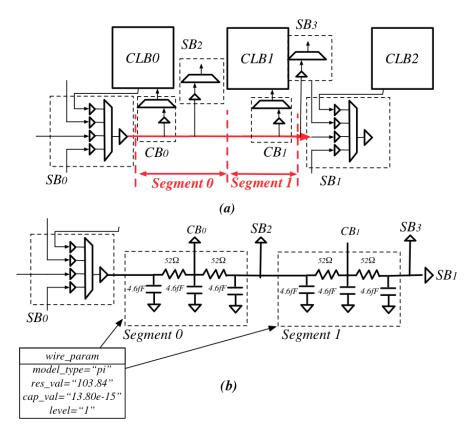

<circuit_model type="chan_wire" name="chan_segment" prefix="track_seg" is_default="true">

<design_technology type="cmos"/>

<input_buffer exist="false"/>

<output_buffer exist="false"/>

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<wire_param model_type="pi" R="101" C="22.5e-15" num_level="1"/> <!-- model_type could_</pre>

→ be T, res_val and cap_val DON'T CARE -->

</circuit_model>

<circuit_model type="wire" name="direct_interc" prefix="direct_interc" is_default="true">

<design_technology type="cmos"/>

<input_buffer exist="false"/>

<output_buffer exist="false"/>

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<wire_param model_type="pi" R="0" C="0" num_level="1"/> <!-- model_type could be T,...</pre>

→res_val cap_val should be defined -->

</circuit_model>

<!-- Atom circuit models end-->

```

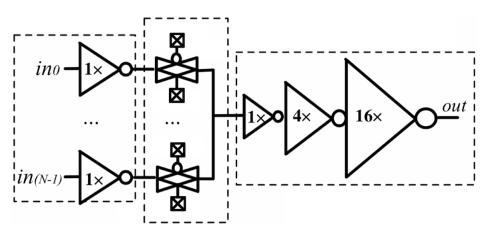

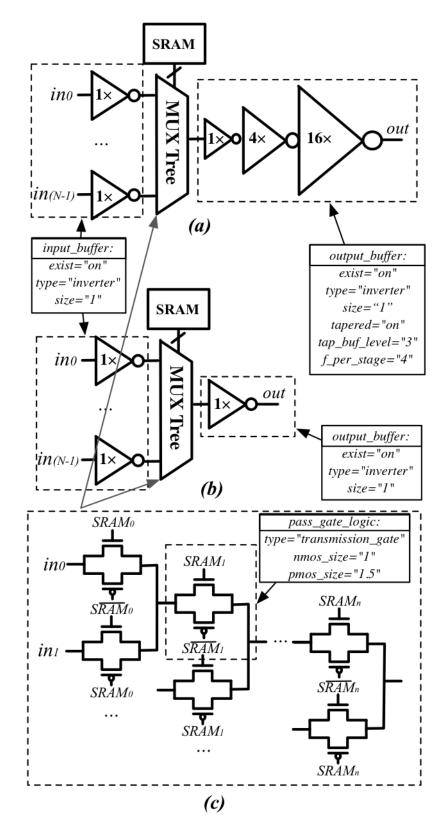

In this tutorial, we require the following primitive <circuit\_model>, which are routing multiplexers, Look-Up Tables, I/O cells in FPGA architecture (see Fig. 5.1).

**Note:** We use different routing multiplexer circuits to maximum the performance by considering it fan-in and fan-out in the architecture context.

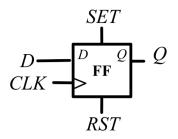

**Note:** We specify that external Verilog netlists will be used for the circuits of Flip-Flops (FFs) static\_dff and sc\_dff\_compact, as well as the circuit of I/O cell iopad. Other circuit models will be auto-generated by OpenFPGA.

```

<!-- Primitive circuit models begin -->

<circuit_model type="mux" name="mux_2level" prefix="mux_2level" dump_structural_verilog=

\rightarrow "true">

<design_technology type="cmos" structure="multi_level" num_level="2" add_const_input=</pre>

'true' const_input_val="1"/>

<input_buffer exist="true" circuit_model_name="INVTX1"/>

<output_buffer exist="true" circuit_model_name="INVTX1"/>

<pass_gate_logic circuit_model_name="TGATE"/>

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<port type="sram" prefix="sram" size="1"/>

</circuit_model>

<circuit_model type="mux" name="mux_2level_tapbuf" prefix="mux_2level_tapbuf" dump_

→structural_verilog="true">

<design_technology type="cmos" structure="multi_level" num_level="2" add_const_input=</pre>

→"true" const_input_val="1"/>

<input_buffer exist="true" circuit_model_name="INVTX1"/>

<output_buffer exist="true" circuit_model_name="tap_buf4"/>

<pass_gate_logic circuit_model_name="TGATE"/>

```

```

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<port type="sram" prefix="sram" size="1"/>

</circuit_model>

<circuit_model type="mux" name="mux_1level_tapbuf" prefix="mux_1level_tapbuf" is_default=

→"true" dump_structural_verilog="true">

<design_technology type="cmos" structure="one_level" add_const_input="true" const_</pre>

→input_val="1"/>

<input_buffer exist="true" circuit_model_name="INVTX1"/>

<output_buffer exist="true" circuit_model_name="tap_buf4"/>

<pass_gate_logic circuit_model_name="TGATE"/>

<port type="input" prefix="in" size="1"/>

<port type="output" prefix="out" size="1"/>

<port type="sram" prefix="sram" size="1"/>

</circuit_model>

<!--DFF subckt ports should be defined as <D> <Q> <CLK> <RESET> <SET> -->

<circuit_model type="ff" name="static_dff" prefix="dff" spice_netlist="${0PENFPGA_PATH}/

→openfpga_flow/SpiceNetlists/ff.sp" verilog_netlist="${OPENFPGA_PATH}/openfpga_flow/

→VerilogNetlists/ff.v">

<design_technology type="cmos"/>

<input_buffer exist="true" circuit_model_name="INVTX1"/>

<output_buffer exist="true" circuit_model_name="INVTX1"/>

<port type="input" prefix="D" size="1"/>

<port type="input" prefix="set" size="1" is_global="true" default_val="0" is_set="true"</pre>

→"/>

<port type="input" prefix="reset" size="1" is_global="true" default_val="0" is_reset=</pre>

→"true"/>

<port type="output" prefix="Q" size="1"/>

<port type="clock" prefix="clk" size="1" is_global="true" default_val="0" />

</circuit_model>

<circuit_model type="lut" name="lut4" prefix="lut4" dump_structural_verilog="true">

<design_technology type="cmos"/>

<input_buffer exist="true" circuit_model_name="INVTX1"/>

<output_buffer exist="true" circuit_model_name="INVTX1"/>

<lut_input_inverter exist="true" circuit_model_name="INVTX1"/>

<lut_input_buffer exist="true" circuit_model_name="buf4"/>

<pass_gate_logic circuit_model_name="TGATE"/>

<port type="input" prefix="in" size="4"/>

<port type="output" prefix="out" size="1"/>

<port type="sram" prefix="sram" size="16"/>

</circuit_model>

<!--Scan-chain DFF subckt ports should be defined as <D> <Q> <Qb> <CLK> <RESET> <SET> --

\rightarrow >

<circuit_model type="ccff" name="sc_dff_compact" prefix="scff" spice_netlist="${OPENFPGA_

→flow/VerilogNetlists/ff.v">

<design_technology type="cmos"/>

<input_buffer exist="true" circuit_model_name="INVTX1"/>

<output_buffer exist="true" circuit_model_name="INVTX1"/>

<port type="input" prefix="pReset" lib_name="reset" size="1" is_global="true" default_</pre>

→val="0" is_reset="true" is_prog="true"/>

<port type="input" prefix="D" size="1"/>

```

```

<port type="output" prefix="Q" size="1"/>

<port type="output" prefix="Qb" size="1"/>

<port type="clock" prefix="prog_clk" lib_name="clk" size="1" is_global="true" default_</pre>

→val="0" is_prog="true"/>

</circuit_model>

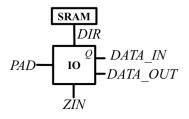

<circuit_model type="iopad" name="iopad" prefix="iopad" spice_netlist="${0PENFPGA_PATH}/

openfpga_flow/SpiceNetlists/io.sp" verilog_netlist="${0PENFPGA_PATH}/openfpga_flow/

→VerilogNetlists/io.v">

<design_technology type="cmos"/>

<input_buffer exist="true" circuit_model_name="INVTX1"/>

<output_buffer exist="true" circuit_model_name="INVTX1"/>

<port type="inout" prefix="pad" size="1" is_global="true" is_io="true"/>

<port type="sram" prefix="en" size="1" mode_select="true" circuit_model_name="sc_dff_</pre>

→compact" default_val="1"/>

<port type="input" prefix="outpad" size="1"/>

<port type="output" prefix="inpad" size="1"/>

</circuit_model>

<!-- Primitive circuit models end -->

```

See details in Circuit Library and Circuit model examples.

#### Annotation on VPR Architecture

In this part, we bind the <circuit\_model> defined in the circuit library to each FPGA component.

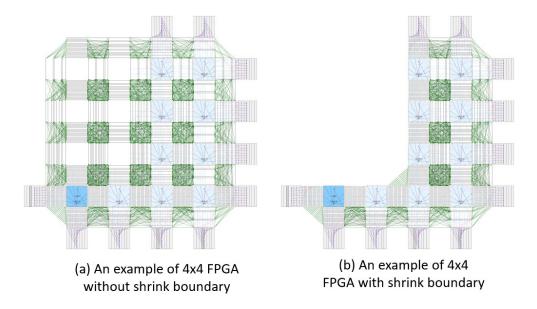

We specify that the FPGA fabric will be configured through a chain of Flip-Flops (FFs), which is built with the <circuit\_model name=sc\_dff\_compact>.

```

<configuration_protocol>

<organization type="scan_chain" circuit_model_name="sc_dff_compact"/>

</configuration_protocol>

```

For the routing architecture, we specify the circuit\_model to be used as routing multiplexers inside Connection Blocks (CBs), Switch Blocks (SBs), and also the routing wires.

```

<connection_block>

<switch name="ipin_cblock" circuit_model_name="mux_2level_tapbuf"/>

</connection_block>

<switch_block>

<switch_name="0" circuit_model_name="mux_2level_tapbuf"/>

</switch_block>

<routing_segment>

<segment name="L4" circuit_model_name="chan_segment"/>

</routing_segment>

```

**Note:** For a correct binding, the name of connection block, switch block and routing segment should match the name definition in your VPR architecture description!

For each <pb\_type> defined in the <complexblocklist> of VPR architecture, we need to specify

• The physical mode for any <pb\_type> that contains multiple <mode>. The name of the physical mode should match a mode name that is defined in the VPR architecture. For example:

<pb\_type name="io" physical\_mode\_name="physical"/>

• The circuit model used to implement any primitive <pb\_type> in physical modes. It is required to provide full hierarchy of the pb\_type. For example:

<pb\_type name="io[physical].iopad" circuit\_model\_name="iopad" mode\_bits="1"/>

**Note:** Mode-selection bits should be provided as the default configuration for a configurable resource. In this example, an I/O cell has a configuration bit, as defined in the <circuit\_model name="iopad">>. We specify that by default, the configuration memory will be set to logic 1.

• The physical <pb\_type> for any <pb\_type> in the operating modes (mode other than the physical mode). This is required to translate mapping results from operating modes to their physical modes, in order to generate bitstreams. It is required to provide full hierarchy of the pb\_type. For example,

```

<pb_type name="io[inpad].inpad" physical_pb_type_name="io[physical].iopad" mode_bits="1"/

>>

```

**Note:** Mode-selection bits should be provided so as to configure the circuits to be functional as required by the operating mode. In this example, an I/O cell will be configured with a logic 1 when operating as an input pad.

• The circuit model used to implement interconnecting modules. The interconnect name should match the definition in the VPR architecture file. For example,

<interconnect name="crossbar" circuit\_model\_name="mux\_2level"/>

**Note:** If not specified, each interconnect will be binded to its default circuit\_model. For example, the crossbar will be binded to the default multiplexer <circuit\_model name="mux\_1level\_tapbuf">, if not specified here.

Note: OpenFPGA automatically infers the type of circuit model required by each interconnect.

The complete annotation is shown as follows:

See details in Bind circuit modules to VPR architecture.

### 5.1.3 Simulation Settings

OpenFPGA needs an XML file where detailed simulation settings are defined. The simulation settings contain critical parameters to build testbenches for verify the FPGA fabric.

You may create an XML file k4\_n4\_openfpga\_simulation.xml and then add contents shown as follows.

The complete annotation is shown as follows:

```

<openfpga_simulation_setting>

<clock_setting>

<operating frequency="auto" num_cycles="auto" slack="0.2"/>

<programming frequency="100e6"/>

</clock_setting>

<simulator_option>

<operating_condition temperature="25"/>

<output_log verbose="false" captab="false"/>

<accuracy type="abs" value="1e-13"/>

<runtime fast_simulation="true"/>

</simulator_option>

<monte_carlo num_simulation_points="2"/>

<measurement_setting>

<slew>

<rise upper_thres_pct="0.95" lower_thres_pct="0.05"/>

<fall upper_thres_pct="0.05" lower_thres_pct="0.95"/>

</slew>

<delay>

<rise input_thres_pct="0.5" output_thres_pct="0.5"/>

<fall input_thres_pct="0.5" output_thres_pct="0.5"/>

</delay>

</measurement_setting>

<stimulus>

<clock>

<rise slew_type="abs" slew_time="20e-12" />

<fall slew_type="abs" slew_time="20e-12" />

</clock>

<input>

<rise slew_type="abs" slew_time="25e-12" />

<fall slew_type="abs" slew_time="25e-12" />

</input>

</stimulus>

</openfpga_simulation_setting>

```

The <clock\_setting> is crucial to create clock signals in testbenches.

**Note:** FPGA has two types of clocks, one is the operating clock which controls applications that mapped to FPGA fabric, while the other is the programming clock which controls the configuration protocol.

In this example, we specify

- the operating clock will follow the maximum frequency achieved by VPR routing results

- the number of operating clock cycles to be used will follow the average signal activities of the RTL design that is mapped to the FPGA fabric.

- the actual operating clock frequency will be relaxed (reduced) by 20% by considering the errors between VPR results and physical designs.

- the programming clock frequency is fixed at 200MHz

The <simulator\_option> are the options for SPICE simulator. Here we specify

- SPICE simulations will consider a 25  $^{\circ}C$  temperature.

- SPICE simulation will output results in a compact way without details on node capacitances.

- SPICE simulation will use 0. 1ps as the minimum time step.

- SPICE simulation will consider fast algorithms to speed up runtime.

The <monte\_carlo num\_simulation\_points="2"/> are the options for SPICE simulator. Here we specify that for each testbench, we will consider two Monte-Carlo simulations to evaluate the impact of process variations.

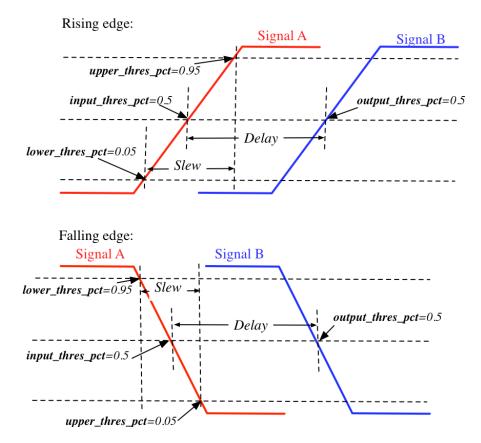

The <measurement\_setting> specify how the output signals will be measured for delay and power evaluation. Here we specify that

- for slew calculation (used in power estimation), we consider from the 5% of the VDD to the 95% of the VDD for both rising and falling edges.

- for delay calculation, we consider from the 50% of the VDD of input signal to the 50% of the VDD of output signals for both rising and falling edges.

In the <stimulus>, we specify that 20ps slew time will be applied to built clock waverforms in SPICE simulations. See details in *Simulation settings*.

# 5.2 Integrating Custom Verilog Modules user defined template.v

### 5.2.1 Introduction and Setup

#### In this tutorial, we will

- Provide the motivation for generating the user\_defined\_template.v verilog file

- Go through a generated user\_defined\_template.v file to demonstrate how to use it

Through this tutorial, we will show how and when to use the *user\_defined\_template.v* file.

To begin the tutorial, we start with a modified version of the hard adder task that comes with OpenFPGA. To follow along, go to the root directory of OpenFPGA and enter:

with

vi openfpga\_flow/openfpga\_arch/k6\_frac\_N10\_adder\_chain\_40nm\_openfpga.xml

Go to LINE187 and replace LINE187 with:

```

<circuit_model type="hard_logic" name="ADDF" prefix="ADDF" is_default="true" spice_

onetlist="${OPENFPGA_PATH}/openfpga_flow/openfpga_cell_library/spice/adder.sp" verilog_netlist="">

```

### 5.2.2 Motivation

From the OpenFPGA root directory, run the command:

Running this command should fail and produce the following errors:

ERROR - iverilog\_verification run failed with returncode 21 ERROR - command iverilog -o compiled\_and2 ./SRC/and2\_include\_netlists.v -s and2\_top\_  $\rightarrow$  formal\_verification\_random\_tb ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF ERROR - -->>././SRC/lb/logical\_tile\_clb\_mode\_default\_\_fle\_mode\_physical\_\_fabric\_mode\_ →default\_\_adder.v:50: error: Unknown module type: ADDF

This error log can also be found by running the following command from the root directory:

This command failed during the verification step because the path to the module definition for **ADDF** is missing. In our architecture file, user-defined verilog modules are those <circuit\_model> with the key term *verilog\_netlist*. The user\_defined\_template.v file provides a module template for incorporating Hard IPs without external library into the architecture.

### 5.2.3 Fixing the Error

This error can be resolved by replacing the LINE187 of k6\_frac\_N10\_adder\_chain\_40nm\_openfpga.xml with the following:

```

<circuit_model type="hard_logic" name="ADDF" prefix="ADDF" is_default="true" spice_

onetlist="${OPENFPGA_PATH}/openfpga_flow/openfpga_cell_library/spice/adder.sp"

overilog_netlist="${OPENFPGA_PATH}/openfpga_flow/openfpga_cell_library/verilog/adder.v">

```

The above line provides a path to generate the *user\_defined\_template.v* file. Now we can return to the root directory and run this command again:

The task should now complete without any errors.

### 5.2.4 Fixing the Error with user\_defined\_template.v

The *user\_defined\_template.v* file can be found starting from the root directory and entering:

**Note:** The user\_defined\_template.v file contains user-defined verilog modules that are found in the openf-pga\_cell\_library with ports declaration (compatible with other netlists that are auto-generated by OpenFPGA) but

without functionality. user\_defined\_template.v is used as a reference for engineers to check what is the port sequence required by top-level verilog netlists. user\_defined\_template.v can be included in simulation only if there are modifications to the user\_defined\_template.v.

To implement our own **ADDF** module, we need to remove all other module definitions (they are already defined elsewhere and will cause an error if left in). Replace the user\_defined\_template.v file with the following:

//-----FPGA Synthesizable Verilog Netlist 11 11 Description: Template for user-defined Verilog modules 11 Author: Xifan TANG 11 Organization: University of Utah 11 Date: Fri Mar 19 10:05:32 2021 //-----//---- Time scale -----`timescale 1ns / 1ps // ----- Template Verilog module for ADDF -----//---- Default net type -----`default\_nettype none // ----- Verilog module for ADDF ----module ADDF(A, Β, CI, SUM, CO); //---- INPUT PORTS ----input [0:0] A; //---- INPUT PORTS ----**input** [0:0] B; //---- INPUT PORTS ----**input** [0:0] CI; //---- OUTPUT PORTS ----output [0:0] SUM; //----- OUTPUT PORTS ----**output** [0:0] CO; //---- BEGIN wire-connection ports -----//---- END wire-connection ports -----//---- BEGIN Registered ports -----//---- END Registered ports -----// ----- Internal logic should start here ----assign SUM = A ^ B ^ CI; assign CO = (A & B) | (A & CI) | (B & CI);// ----- Internal logic should end here ----endmodule // ----- END Verilog module for ADDF -----

We can now link this user\_defined\_template.v into k6\_frac\_N10\_adder\_chain\_40nm\_openfpga.xml.

Note: Be sure to select the run where you modified the user\_defined\_template.v!

From the OpenFPGA root directory, run:

vi openfpga\_flow/openfpga\_arch/k6\_frac\_N10\_adder\_chain\_40nm\_openfpga.xml

At **LINE187** in verilog\_netlist, put in:

Finally, rerun this command from the OpenFPGA root directory to ensure it is working:

## 5.3 Build an FPGA fabric using Standard Cell Libraries

### 5.3.1 Introduction

#### In this tutorial, we will

- Showcase how to create an architecture description based on standard cells, using OpenFPGA's circuit modeling language

- Use Skywater's Process Design Kit (PDK) cell library to create an OR Gate circuit model for OpenFPGA

- Verify that the standard cell library file was correctly bound into the selected architecture file by looking at auto-generated OpenFPGA files and checking simulation waveforms in GTKWave

Through this example, we will show how to bind standard cell library files with OpenFPGA Architectures.

**Note:** We showcase the methodology by considering the open-source Skywater 130nm PDK so that users can easily reproduce the results.

#### 5.3.2 Create and Verify the OpenFPGA Circuit Model

**Note:** In this tutorial, we focus on binding a 2-input **OR** gate from a standard cell library to a circuit model in OpenFPGA's architecture description file. Note that the approach can be generalized to any circuit model.

For this tutorial, we start with an example where the HDL netlist of an 2-input **OR** gate that is auto-generated by OpenFPGA. After updating the architecture file, the auto-generated HDL netlist created by OpenFPGA will directly instantiate a standard cell from the open-source Skywater 130nm PDK library. To follow along, go to the root directory of OpenFPGA and enter:

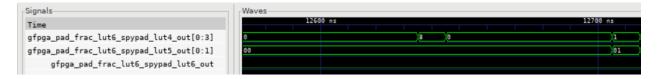

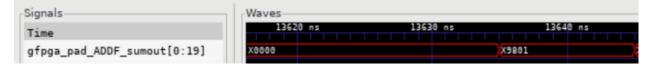

This will run a prebuilt task with OpenFPGA cell libraries. When the task is finished, there will be many auto-generated files to look through. For this tutorial, we are interested in the luts.v and and2\_formal.vcd files. The **OR2** gate is used as a control circuit in the **lut6** circuit model, and the and2\_formal.vcd file will have the resulting waveforms from the simulation run by the task. To open the luts.v file, run the following command:

Note: Users can find full details about netlist organization in our documentation: Fabric Netlists

The luts.v file represents a Look Up Table within the OpenFPGA architecture. The important lines of this file for the tutorial are highlighted below. These lines show the instantiation of OpenFPGA's **OR2** cell library.

```

//-----

//

FPGA Synthesizable Verilog Netlist

//

Description: Look-Up Tables

// Author: Xifan TANG

// Organization: University of Utah

// Date: Tue Mar 30 15:25:03 2021

//-----

//---- Time scale -----

`timescale 1ns / 1ps

//---- Default net type -----

default_nettype none

// ----- Verilog module for frac_lut6 -----

module frac_lut6(in,

sram,

sram_inv,

mode,

mode_inv,

lut4_out,

lut5_out,

lut6_out);

//---- INPUT PORTS -----

input [0:5] in;

//---- INPUT PORTS -----

input [0:63] sram;

//----- INPUT PORTS -----

input [0:63] sram_inv;

//---- INPUT PORTS -----

input [0:1] mode;

//----- INPUT PORTS -----

input [0:1] mode_inv;

//---- OUTPUT PORTS -----

output [0:3] lut4_out;

//---- OUTPUT PORTS -----

output [0:1] lut5_out;

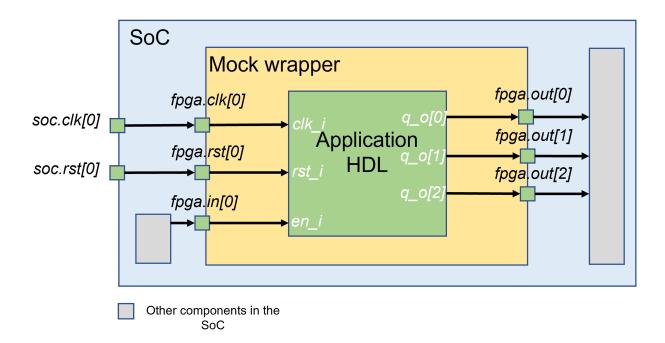

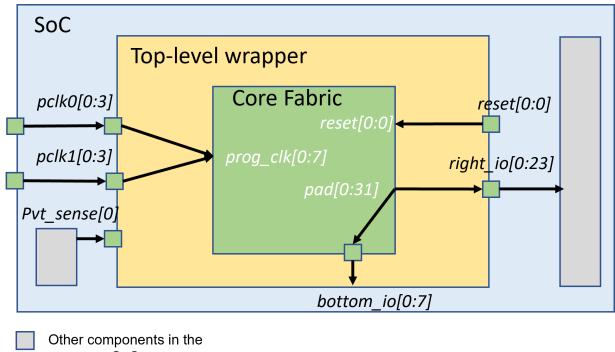

```