Fabric Netlists

In this part, we will introduce the hierarchy, dependency and functionality of each Verilog netlist, which are generated to model the FPGA fabric.

Note

These netlists are automatically generated by the OpenFPGA command write_fabric_verilog. See FPGA-Verilog for its detailed usage.

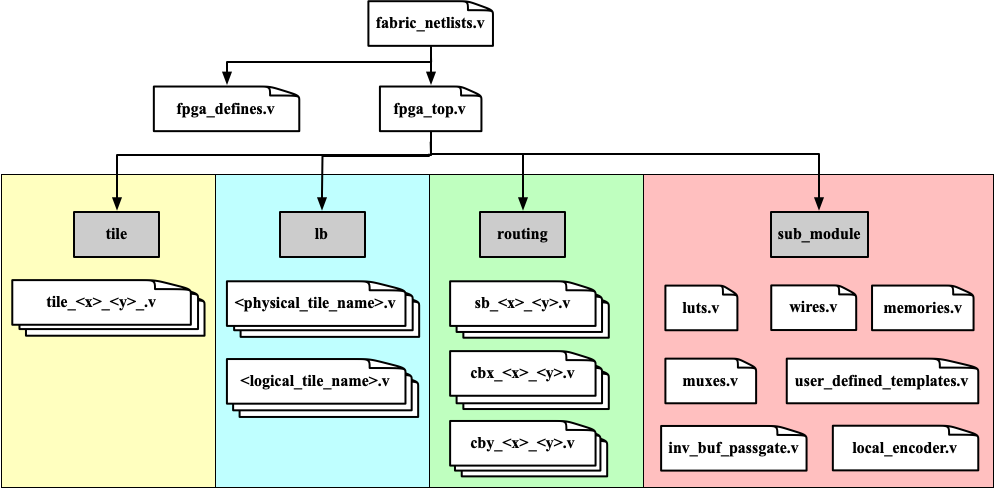

All the generated Verilog netlists are located in the directory as you specify in the OpenFPGA command write_fabric_verilog. Inside the directory, the Verilog netlists are organized as illustrated in Fig. 69.

Fig. 69 Hierarchy of Verilog netlists modeling a FPGA fabric

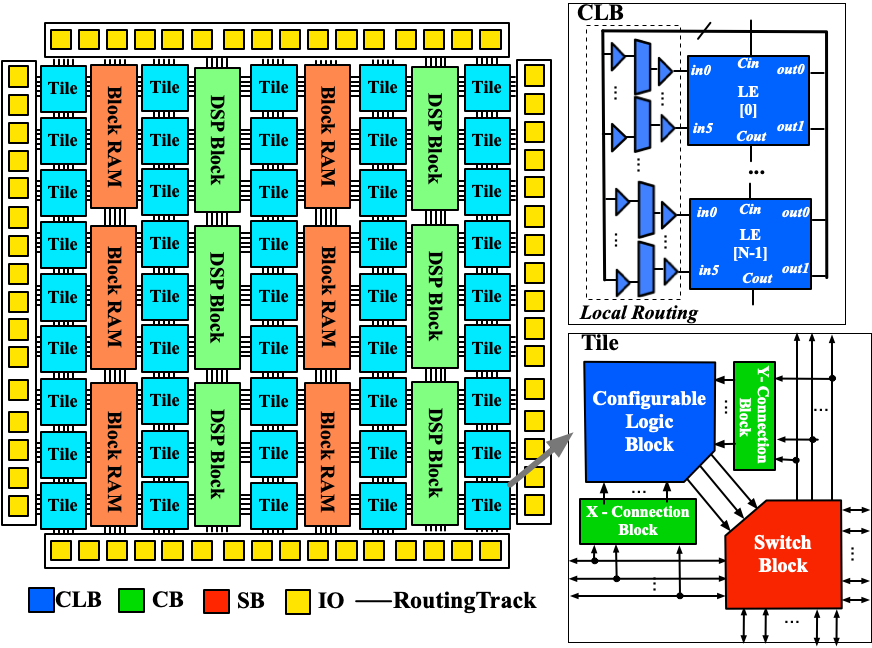

Fig. 70 An illustrative FPGA fabric modelled by the Verilog netlists

Top-level Netlists

- fabric_netlists.v

This file includes all the related Verilog netlists that are used by the

fpga_top.v. This file is created to simplify the netlist addition for HDL simulator and backend tools. This is the only file you need to add to a simulator or backend project.Note

User-defined (external) Verilog netlists are included in this file.

- fpga_top.v

This netlist contains the top-level module of the fpga fabric, corresponding to the fabric shown in Fig. 70.

- fpga_defines.v

This file includes pre-processing flags required by the

fpga_top.v, to smooth HDL simulation. It will include the folliwng pre-procesing flags:`define ENABLE_TIMINGWhen enabled, all the delay values defined in primitive Verilog modules will be considered in compilation. This flag is added when--include_timingoption is enabled when calling thewrite_fabric_verilogcommand.

Note

We strongly recommend users to turn on this flag as it can help simulators to converge quickly.

Tiles

This sub-directory contains all the tile-level modules. Only seen when the --group_tile option is enabled when calling command build_fabric.

Each tile groups a number of programmable blocks (Logic Blocks) and routing blocks (Routing Blocks), as depicted in Fig. 70.

Tiles are instanciated under the top-level module (Top-level Netlists).

- tile_<x>__<y>_.v

For each unique tile, a Verilog netlist will be generated. The

<x>and<y>denote the coordinate of the tile in the FPGA fabric.

Logic Blocks

This sub-directory contains all the Verilog modules modeling configurable logic blocks, heterogeneous blocks as well as I/O blocks. Take the example in Fig. 70, the modules are CLBs, DSP blocks, I/Os and Block RAMs.

- <physical_tile_name>.v

For each

<physical_tile>defined in the VPR architecture description, a Verilog netlist will be generated to model its internal structure.Note

For I/O blocks, separated

<physical_tile_name>.vwill be generated for each side of a FPGA fabric.

- <logical_tile_name>.v

For each root

pb_typedefined in the<complexblock>of VPR architecture description, a Verilog netlist will be generated to model its internal structure.

Routing Blocks

This sub-directory contains all the Verilog modules modeling Switch Blocks (SBs) and Connection Blocks (CBs). Take the example in Fig. 70, the modules are the Switch Blocks, X- and Y- Connection Blocks of a tile.

- sb_<x>_<y>.v

For each unique Switch Block (SB) created by VPR routing resource graph generator, a Verilog netlist will be generated. The

<x>and<y>denote the coordinate of the Switch Block in the FPGA fabric.

- cbx_<x>_<y>.v

For each unique X-direction Connection Block (CBX) created by VPR routing resource graph generator, a Verilog netlist will be generated. The

<x>and<y>denote the coordinate of the Connection Block in the FPGA fabric.

- cby_<x>_<y>.v

For each unique Y-direction Connection Block (CBY) created by VPR routing resource graph generator, a Verilog netlist will be generated. The

<x>and<y>denote the coordinate of the Connection Block in the FPGA fabric.

Primitive Modules

This sub-directory contains all the primitive Verilog modules, which are used to build the logic blocks and routing blocks.

- luts.v

Verilog modules for all the Look-Up Tables (LUTs), which are defined as

<circuit_model name="lut">of OpenFPGA architecture description. See details in Circuit Library.

- wires.v

Verilog modules for all the routing wires, which are defined as

<circuit_model name="wire|chan_wire">of OpenFPGA architecture description. See details in Circuit Library.

- memories.v

Verilog modules for all the configurable memories, which are defined as

<circuit_model name="ccff|sram">of OpenFPGA architecture description. See details in Circuit Library.

- muxes.v

Verilog modules for all the routing multiplexers, which are defined as

<circuit_model name="mux">of OpenFPGA architecture description. See details in Circuit Library.Note

multiplexers used in Look-Up Tables are also defined in this netlist.

- inv_buf_passgate.v

Verilog modules for all the inverters, buffers and pass-gate logics, which are defined as

<circuit_model name="inv_buf|pass_gate">of OpenFPGA architecture description. See details in Circuit Library.

- local_encoder.v

Verilog modules for all the encoders and decoders, which are created when routing multiplexers are defined to include local encoders. See details in Circuit model examples.

- user_defined_templates.v

This is a template netlist, which users can refer to when writing up their user-defined Verilog modules. The user-defined Verilog modules are those

<circuit_model>in the OpenFPGA architecture description with a specificverilog_netlistpath. It contains Verilog modules with ports declaration (compatible to other netlists that are auto-generated by OpenFPGA) but without any functionality. This file is created only when the option--print_user_defined_templateis enabled when calling thewrite_fabric_verilogcommand.Warning

Do not include this netlist in simulation without any modification to its content!